PLL (Phase Locked Loop)

PLL(Phase-Locked Loop)은 전자 회로의 한 종류로서, 입력 클록 신호의 위상(Phase)을 지속적으로 추적하고 맞추어,

안정적인 주파수 와 위상을 가진 출력 클럭 신호를 생성하는 시스템이다.

PLL은 주파수를 높이거나 낮추고 클럭 신호를 정확하게 동기화하는데 사용된다.

이는 특히 통신, 컴퓨터, 기타 디지털 장치에서 중요한 역할을 한다.

PLL의 주요 구성 요소는 다음과 같다.

- 위상 검출기(Phase Detector):

입력 클럭과 VCO(전압제어 발진기) 출력 클럭 차이의 위상 차이를 검출 한다. - 루프 필터(Loop Filter):

위상 검출기에서 나온 신호를 안정화시켜, VCO를 제어하는 데 적합한 형태로 변환한다. - VCO(Volatage Controlled Oscillator):

루프 필터에서 제어 신호를 받아, 주파수가 조절 가능한 출력 클럭을 생성한다.

PLL의 작동 방식은 다음과 같다.

- 입력 클럭과 VCO에서 생성된 클럭 사이의 위상 차이를 위상 검출기가 감지한다.

- 이 위상 차이는 루프 필터를 통해 조절되며, 이것이 VCO를 제어한다.

- VCO는 위상 검출기가 감지한 차이를 최소화하기 위해 주파수를 조정한다.

- 최종적으로, VCO의 출력 클럭은 입력 클럭과 동일한 주파수와 위상을 갖게 된다.

결과적으로 PLL은 입력 클럭에 정확히 동기화된 안정적인 출력 클럭을 제공한다.

Phase Locked Loop(PLL)을 이해하기 쉽게 설명하자면, 음악 밴드에 비유할 수 있다.

밴드에서 드러머는 박자를 맞추는 중요한 역할을 한다.

만약 다른 밴드 멤버들이 드러머의 박자에 맞춰 연주한다면, 모든 연주는 완벽하게 동기화되어 조화로운

연주를 가능하게 한다.

위상 검출기(Phase Detector) 는 밴드 멤버들이 드러머의 박자를 얼마나 잘 따르는지 확인하는 '박자 감지기'이다.

루프 필터(Loop Filter) 는 밴드 멤버들이 조금이라도 박자가 어긋날 때 이를 조정해주는 '조율사' 역할을 한다.

VCO 는 드러머로, 루프 필터의 조율에 따라 박자(주파수)를 빠르게 하거나 느리게 할 수 있다.

- - PLL(Phase Locked Loop) 설정 관련

- PLL Source Mux(PLL 소스 다중화):

MicroController의 주 클럭 소스를 선택한다. HSI와 HSE가 있다. High-Speed Internal, External

(밴드가 연주할 노래를 선택하는 것과 같다. HSE는 외부에서 새로운 노래(클럭 신호를) 가져오는 것이다.) - '/M':

이것은 들어오는 클럭 신호를 작은 숫자로 나누어 주파수를 낮추는 역할을 한다.

너무 높은 주파수를 적절한 수준으로 줄여준다.

(드러머가 너무 빠르게 연주해서 밴드 멤버들이 따라오기 힘들 때, 드러머가 템포를 조금 늦추는 것과 같다.)

(분모(Divisor)를 나타내어 입력 클럭 주파수를 낮춰 작동 범위 내로 맞추는데 사용된다.) - '/N':

PLL의 VCO(Voltage-Controlled Oscillator)를 구동하는 곱셈 인자이다.

이 값은 VCO의 출력 주파수를 결정한다.

(낮춘 주파수를 다시 높여주는 역할을 한다.)

(느린 템포의 곡을 다시 빠르게 만들어 주는 역할을 하는 것이라고 보면 된다.) - '/P':

PLL의 최종 출력 주파수를 결정하는 분주비이다.

이것은 시스템 클록(SYTEM CLOCK:SYSCLK)을 구성하는데 사용된다.

마지막으로, 이 과정에서 만들어진 높은 주파수를 다시 조절하여, 마이크로컨트롤러의 주클럭으로 쓸

최종 주파수를 결정하는 곳이다.

(마지막으로 밴드리더가 노래의 전체 템포를 조절하여 가장 적합한 템포로 만드는 것과 같다.)

- PLL Source Mux(PLL 소스 다중화):

입력 주파수: 25MHz

HSE(High speed External)로 설정

System Clock 은 (입력주파수/M) * N / P가되어 150MHz가 된다.

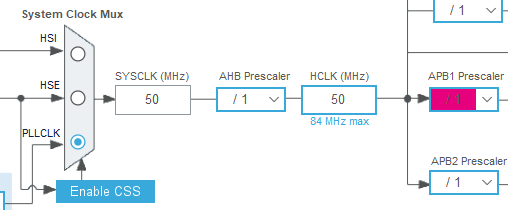

- SYSCLK(MHz):

시스템 클록의 최종 주파수로,

이것은 MicroController의 핵심 클록 주파수로 CPU와 대부분의 내부 주변장치가 이 클록을 사용한다.

SYSCLK는 시스템 전반적인 성능을 결정하는 주요 클록으로,

이 클록의 속도는 마이크로컨트롤러의 작동 속도를 결정한다.

AHB Prescaler

AHB(Advanced High performance bus) 버스의 클록을 나누는 분주비이다.

이것은 HCLK(AHB Clock)을 결정한다.

이렇게 서로 다른 클록 신호를 사용함으로서, 마이크로컨트롤러는 더 효율적인 전력 관리와 성능 최적화를 달성할 수 있다.

Peripheral Clocks

APB Prescaler (Advanced Peripheral Bus) 의 클록을 나누는 분주비이다.

APB Prescaler는 밴드에서 특정악기 (현악기, 금관악기 등) 의 템포를 조절하는 것과 같다.

따라서 Peripheral Clocks는 각 섹션의 각기들이 실제로 어떤 템포로 연주하고 있는지를 나타낸다.

입력 주파수에 따른 장단점

- 낮은 입력 주파수(예: 4MHz)

- 장점:

- 전력 소비 감소:

일반적으로 낮은 주파수는 전력 소비를 줄일 수 있어, 배터리 구동 장치나 저전력 애플리케이션에 적합하다. - 전자파(EMI) 감소:

낮은 주파수는 전자파 간섭을 감소시켜, 무선 통신이 중요한 시스템에서 유리할 수 있다.

- 전력 소비 감소:

- 단점:

- 클록 속도 제한:

낮은 주파수는 PLL을 통해 더 높은 주파수로 변환해야 하는데, 이는 시스템의 최대 클록 속도를 제한할 수 있다. - 응답 시간 증가:

낮은 클록 주파수는 시스템의 반응 시간과 처리 능력을 감소시킬 수 있다.

- 클록 속도 제한:

- 장점:

- 높은 입력 주파수(예: 26MHz)

- 장점:

- 높은 시스템 성능:

높은 입력 주파수는 시스템의 클록 속도를 증가시켜, 더 빠른 처리 속도와 반응 시간을 제공한다. - PLL 설정 유연성:

높은 주파수는 PLL 설정에 더 많은 유연성을 제공하며,

다양한 시스템 요구 사항에 맞게 클록 속도를 쉽게 조정할 수 있다.

- 높은 시스템 성능:

- 단점:

- 전력 소비 증가:

일반적으로 높은 클럭 주파수는 더 많은 전력을 소비한다. - EMI 증가:

높은 주파수는 전자파 간섭을 증가시킬 수 있어, 간섭에 민감한 애플리케이션에서 문제가 될 수 있다.

- 전력 소비 증가:

- 장점:

따라서 입력 주파수의 선택은 애플리케이션의 요구 사항, 전력 소비, 성능 요구사항, EMI 고려 사항 등을 종합적으로 고려하여 결정해야 한다. 낮은 주파수는 저전력, 높은 주파수는 고성능 애플리케이션에 더 적합할 수 있다.

'Firmware & Embedded > ARM' 카테고리의 다른 글

| Linker Script - Memory (0) | 2024.01.07 |

|---|---|

| Code Formatter Profile (0) | 2024.01.06 |

| To build a simple build process (0) | 2024.01.01 |

| Creation and Process of Object Files (0) | 2023.12.31 |

| Chipset 의 이해 (0) | 2023.12.23 |